Basic physics parameter for switching&dissipation

Defined in the paper (Manipatruni-Nikonov), the figure of merit $ \lambda $ for any tunneling junction/CMOS transistor/switch/MtJ

$$ \lambda = \frac{E_{dissipation}}{E_{barrier}} $$

where $ E_{dissipation} \approx E_{switching} $ is the dissipation energy, which is also approximately equal switching energy.

- notice that $ E_{barrier} $ is always around $1-1.5 eV$, so $\lambda$ is really determined by collective versus single-electron physics mechanism and the size of the cell (anything else basic?)

In another paper (Wang - Koester) , the authors argue that $ \lambda \approx 1 $ is achievable. In particular, GSHE looks better than stt-MRAM. AFM and TI (at room temperature) can make significant breakthroughs, especially when made commercial (no sooner than 5 years?).

-

for the electronic-charge switch, $\lambda $ is of order $ N_e \sim 400 $.

-

for stt-MRAM, $ \lambda_{stt-mram} > 1000 $ is indicated, while in 2014 (from Wang-Koester) we can see $ \lambda_{stt-mram} \approx 4 * 10^5 $. This means that basic STT-MRAM is not particularly energy-efficient. From the table on IMComputing page., the review in 2019 we can see $ \lambda_{stt-mram} \approx 10^4 $.

the summary - the smaller the dimensionless parameter $ \lambda $ is the better. This parameter must be larger than 1 for any classical switching. Different switching devices need to optimize this parameter, both CMOS and stt-mram are not at the possible, but very difficul physics-allowed, limit of this parameter.

key figures from the paper (Wang - Koester)

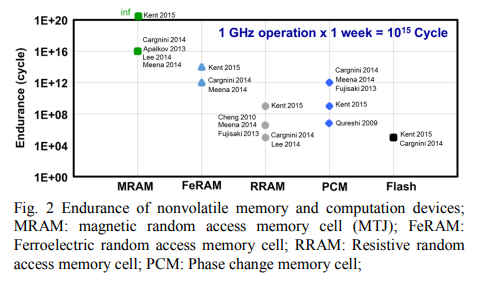

- excellent endurance of stt-MRAM (as well as commercial development)

stt-mram has the best endurance among emerging NVMs, still behind by 1-2 orders of magnitude from SRAM and DRAM, see IMComputing

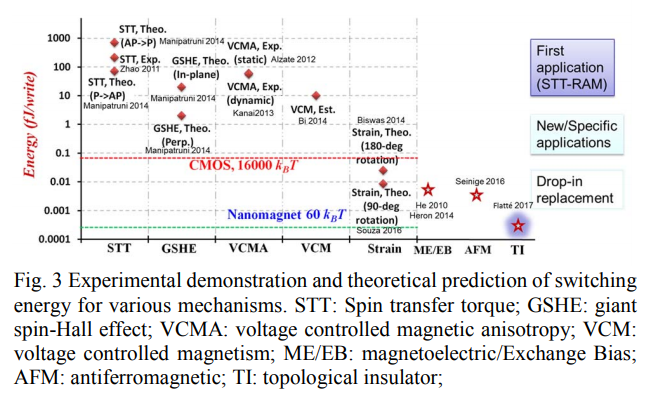

- Switching energy per write operation for stt-MRAM is a severe limitation due to $ \lambda_{stt-mram} > 1000 $

Write energy of stt-mram is about 2 orders of magnitude worse than for CMOS (1600 kT line). stt-mram does not have here advantage against charge-based DRAM and SRAM in spite of being “collective spintronic switch”. SRAM is about 2 orders better in write energy than stt-mram, as you can see from the picture above.

Topological Insulator and Sraintronics-based predicted to be very energy-efficient, but very far from being commercially ready (while in 2021y)

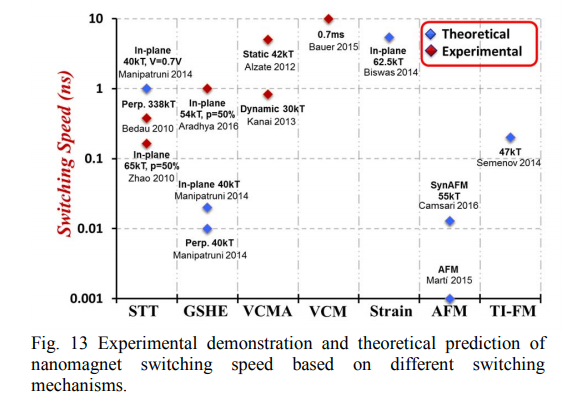

- the challenge of switching speed

distinguish between theoretical and realised versions

stt-mram is the best among experimentally shown to work.

stt- mram is slightly behind in write/read speed than SRAM (the fastest), but close (within 1 order of magnitude).

AFM might become really good both in the switching energy category and the switching speed!

- speed and energy efficiency are two main goals for computing (AI hardware), so far as cost, non-volatility, and endurance are satisfactory (from the point of view of business applications)

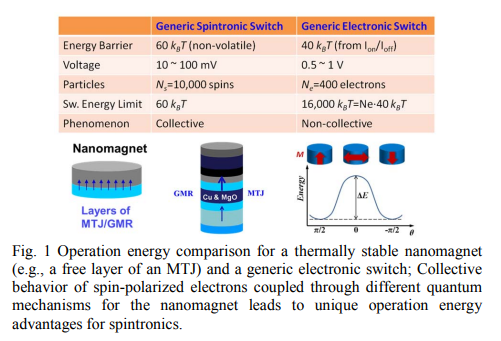

the picture below shows "the ideal collective spintronic switch"

The fundamental advantage of this approach over the semiconductor-based switch concept is its projected low operation energy.

Fig. 1 compares a generic spintronic switch and a generic electronic switch.

The picture might be misunderstood. stt-mram is NOT the “ideal collective spintronic switch”.